Логические триггеры: схемы, типы, устройство, назначение

Логические триггеры что это?

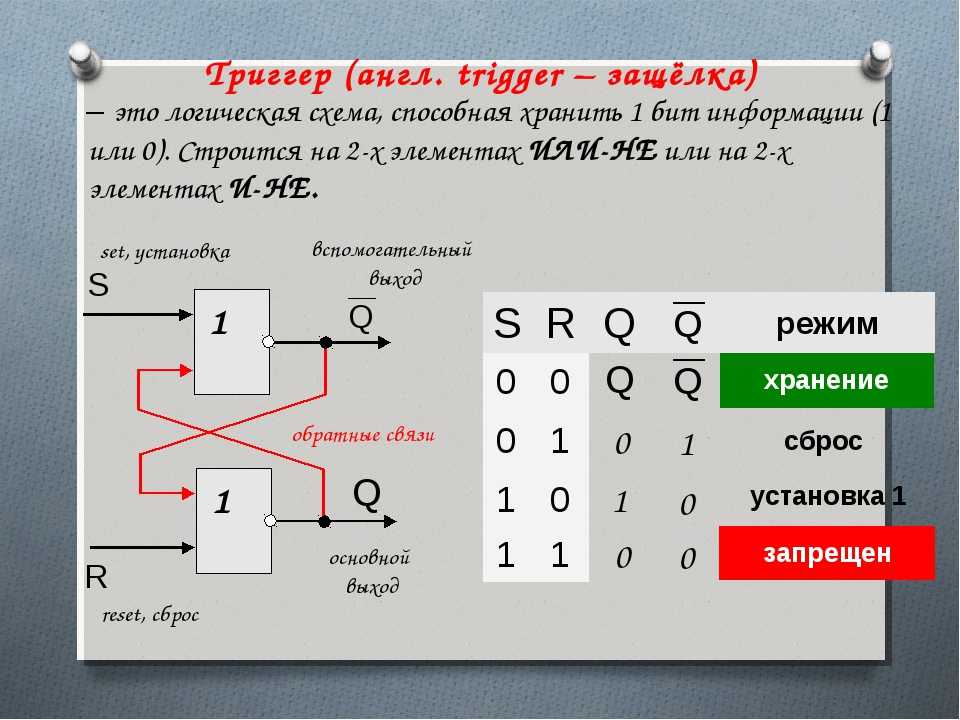

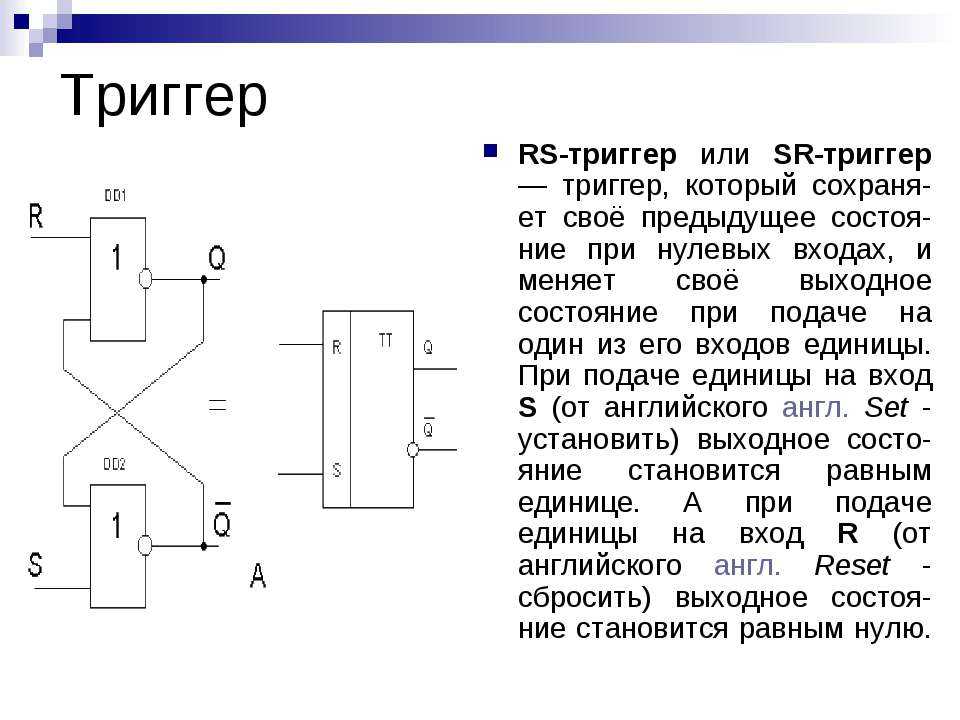

Триггер — простейшее последовательностное устройство, которое может находиться в одном из двух возможных состояний и переходить из одного состояния в другое под воздействием входных сигналов. Триггер является базовым элементом последовательностных логических устройств. Входы триггера разделяют на информационные и управляющие (вспомогательные). Это разделение в значительной степени условно. Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации.

Васильев Дмитрий ПетровичПрофессор электротехники СПбГПУЗадать вопрос Триггеры могут иметь 2 выхода: прямой Q и инверсный Q.

Триггеры классифицируют по различным признакам, поэтому существует достаточно большое число классификаций. К сожалению, эти классификации не образуют стройной системы, но инженеру необходимо их знать.

Классификация триггеров

- по способу приема информации;

- по принципу построения;

- по функциональным возможностям.

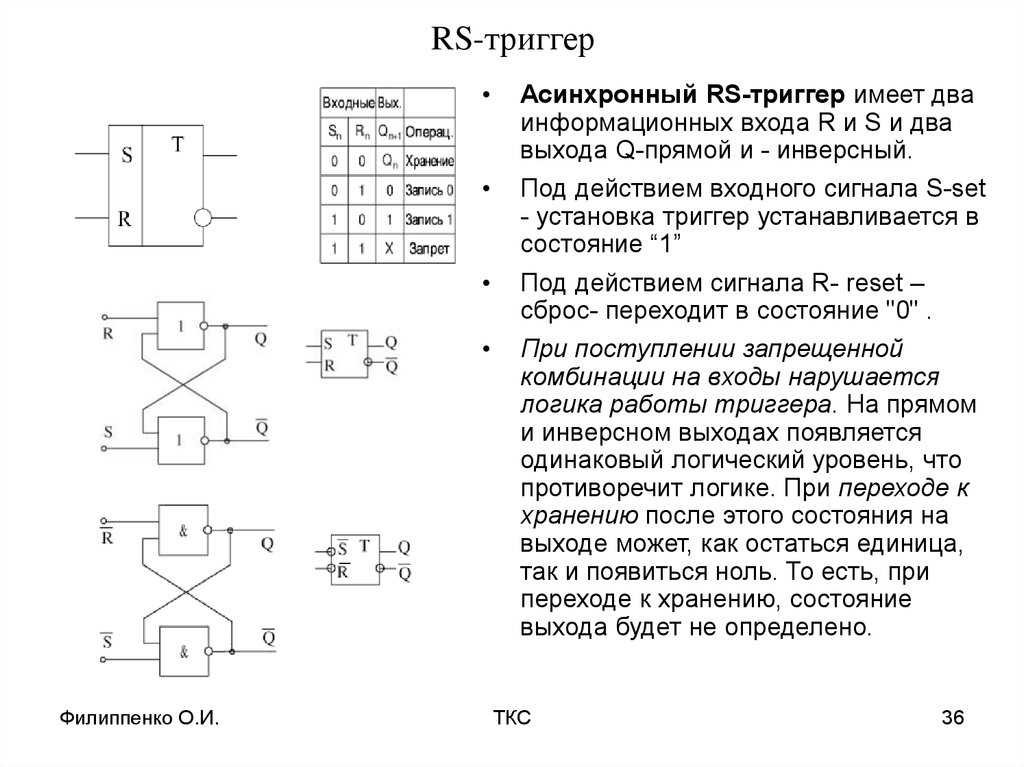

Асинхронный триггер

Асинхронный триггер — изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Васильев Дмитрий ПетровичПрофессор электротехники СПбГПУ Синхронные триггеры — реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации C (от англ. clock). Этот вход также обозначают терминами «строб», «такт».

Синхронные триггеры

Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации C. Статические триггеры воспринимают информационные сигналы при подаче на вход C логической единицы (прямой вход) или логического нуля (инверсный вход).

Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе C от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

Статические триггеры

Статические триггеры в свою очередь подразделяют на одноступенчатые (однотактные) и двухступенчатые (двухтактные). В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают через ТТ.

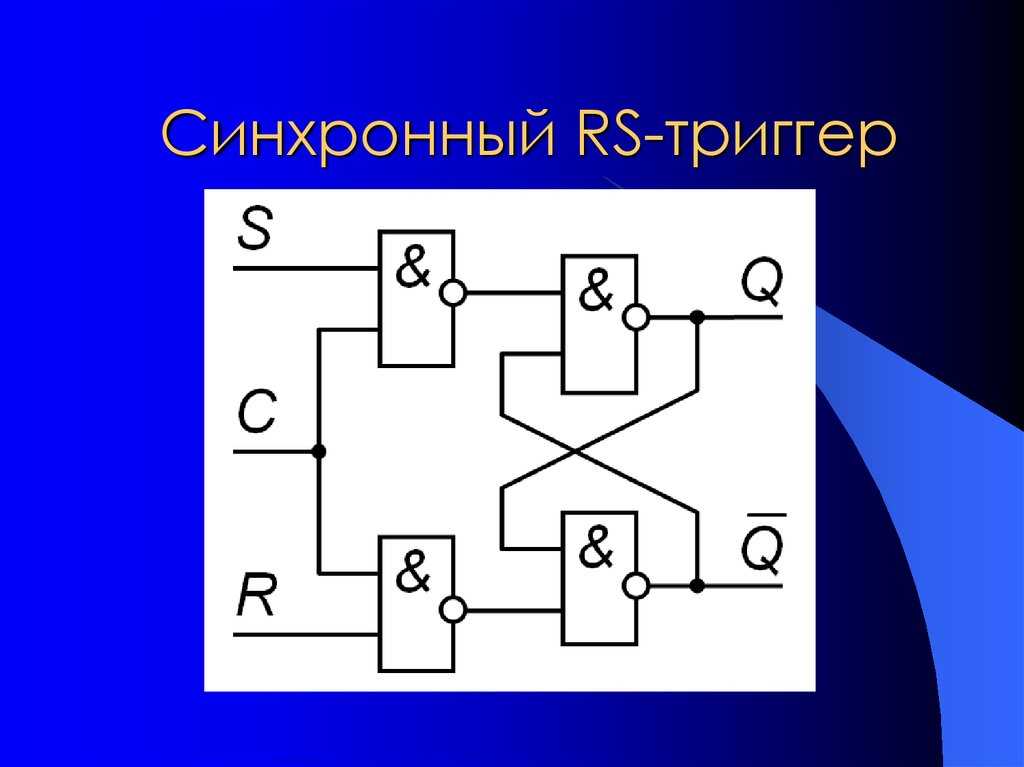

Cинхронные схемы

Бывает, требуется применять схемы с логическими элементами, работающими на основе изменения состояния при создании специальных условий, не зависящих от статуса входов. При этом в схему добавляется логический компонент И, имеющий 2 входа и соединенный с триггерными входами. Теперь входы R и S будут выполняться через терминал И, имеется также третий вход для тактовых импульсов. Изменение работы триггера заключается в том, что на Q̃ и Q состояние будет варьироваться из-за прохождения высокого тактового сигнала на входе, называемого «включить».

Синхронная схема RS триггера

- Когда тактовый сигнал равен 0, выходные значения элементов И идентичны, фиксируя выходные сигналы в последнем запомнившимся статусе;

- При тактовом импульсе, соответствующем единице, вся схема приобретает прозрачность и начинает работать как нормальный РС триггер. При этом оба входа воспринимают сигналы R и S.

Основным преимуществом тактового сигнала является то, что выход этого триггера можно синхронизировать со многими другими схемами и устройствами, которые используют одни и те же тактовые импульсы. Эта компоновка используется для базового расположения памяти, например, применяя различные логические состояния к диапазону из восьми триггеров, а затем посредством синхронного тактового импульса заставляя систему хранить байт данных.

Временные диаграммы

Скважность импульсов

Таблицы истинности иногда не являются лучшим методом описания последовательной схемы. Часто предпочтительнее временная диаграмма синхронизации, которая показывает, как логические состояния в разных точках цепи меняются со временем.

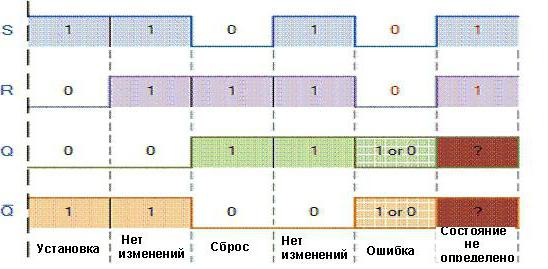

Временная диаграмма RS триггера

На рисунке видно, что в первый момент времени t1 оба сигнала высокие, что вызывает неопределенное состояние. Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

Модифицируем схему триггера

Как мы видели выше, базовые элементы И-НЕ рассмотренного RS-триггера работают так, что при его установке Q̃ = 1 и Q = 0, а при его сбросе Q̃ = 0 и Q = 1, хотя логичнее было бы в первом состоянии иметь Q = 1, а во втором — Q = 0. При этом еще и получается, что смена состояний происходит при падении уровня сигнала с 1 до 0.

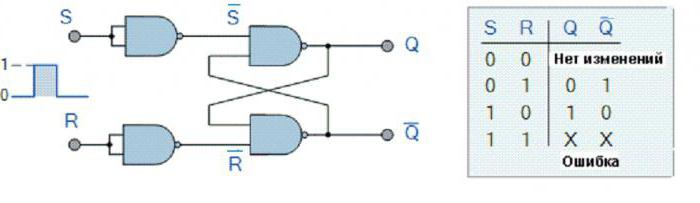

Таким образом, для правильной работы схемы триггера его входные сигналы нужно проинвертировать. Тогда переключения его состояний будут происходить при подаче положительных входных сигналов. Для этого в схему нужно добавить два дополнительных И-НЕ элемента, присоединенных как инверторы к S̃- и R̃-входам, как показано на рисунке ниже. Здесь на входах элементов И-НЕ уже представлены инверсные входные сигналы.

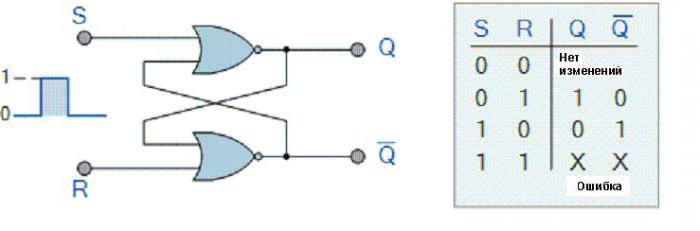

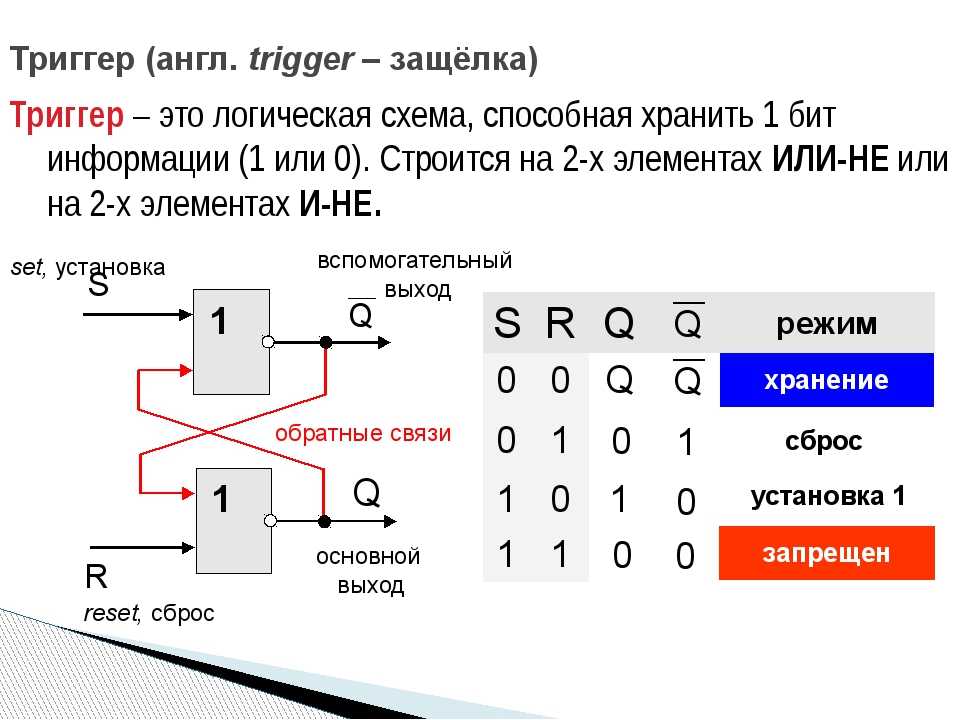

Так же, как и с использованием И-НЕ элементов, можно построить простой RS-триггер с использованием двух ИЛИ-НЕ элементов, соединенных по такой же схеме. Она будет работать аналогичным образом, как и рассмотренная выше схема И-НЕ. При этом активным является высокий уровень сигналов на входах, а недопустимое состояние возникает, когда на оба входа подан уровень логической «1», как это показано в таблице истинности на рисунке ниже.

Различие триггеров по функциональным возможностям

- с раздельной установкой состояния 0 и 1 (RS-триггеры);

- универсальные (JK-триггеры);

- с приемом информации по одному входу D (D-триггеры, или триггеры задержки);

- со счетным входом Т (Т-триггеры).

Обозначение входов триггеров

Входы триггеров обычно обозначают следующим образом:

S — вход для установки в состояние «1»;

R — вход для установки в состояние «0»;

J — вход для установки в состояние «1» в универсальном триггере;

К — вход для установки в состояние «0» в универсальном триггере;

Т — счетный (общий) вход;

D — вход для установки в состояние «1» или в состояние «0»;

V — дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V).

Рассмотрим некоторые типы триггеров и их реализацию на логических элементах.

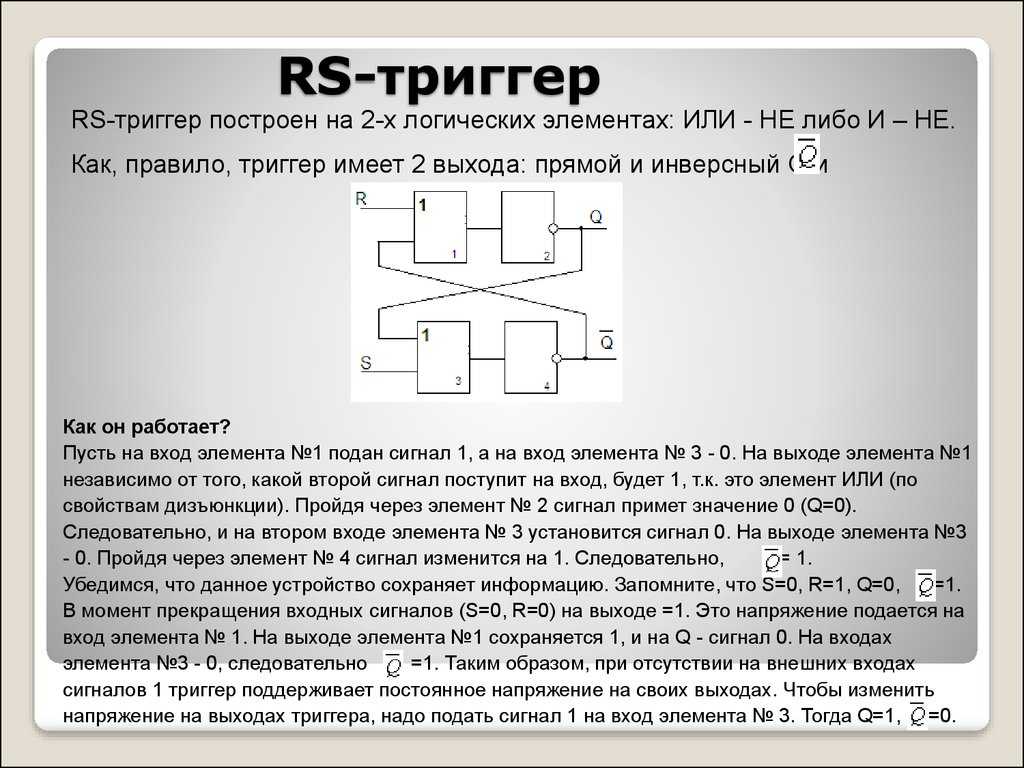

Асинхронный RS-триггер

Обратимся к асинхронному RS-триггеру, имеющему условное графическое обозначение, приведенное на рис. 3.54.

Триггер имеет два информационных входа: S (от англ. set) и R (от англ. reset).

Закон функционирования триггеров удобно описывать таблицей переходов, которую иногда также называют таблицей истинности (рис. 3.55). Через S’, R’, Q’ обозначены соответствующие логические сигналы, имеющие место в некоторый момент времени t, а через Qt + 1 — выходной сигнал в следующий момент времени t+1.

Комбинацию входных сигналов S’ = l, R’ =1 часто называют запрещенной, так как после нее триггер оказывается в состоянии (1 или 0), предсказать которое заранее невозможно. Подобных ситуаций нужно избегать.

Рассматриваемый триггер может быть реализован на двух элементах ИЛИ-НЕ (рис. 3.56).

Необходимо убедиться, что эта схема функционирует в полном соответствии с приведенной выше таблицей переходов.

Микросхема К564ТР2 содержит 4 асинхронных RS-триггера и один управляющий вход (рис. 3.57).

Абрамян Евгений ПавловичДоцент кафедры электротехники СПбГПУ При подаче на вход V низкого уровня выходы триггеров отключаются от выводов микросхем и переходят в третье так называемое высокоимпедансное состояние. При подаче на вход V логического сигнала «1» триггеры работают в соответствии с вышеприведенной таблицей переходов.

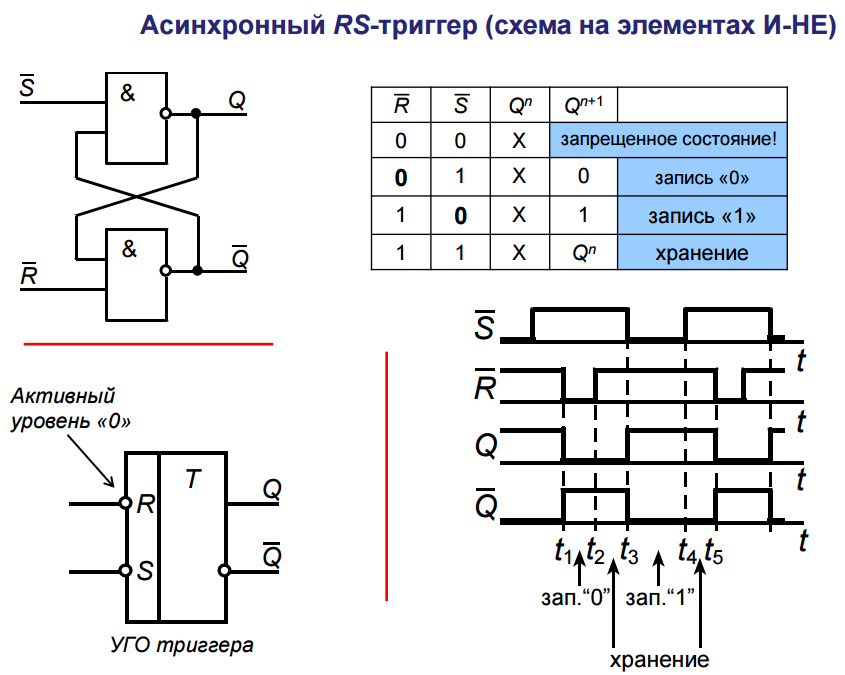

В асинхронном RS-триггере на элементах И-НЕ переключение производится логическим «0», подаваемым на вход R или S, т. е. реализуется обратная рассмотренной ранее таблица переходов (рис. 3.58). Запрещенная комбинация соответствует логическим «0» на обоих входах.

Состояние «Сброшен»

В этом втором устойчивом состоянии Q̃ = 0, а Q = 1, и задается оно входами R = 1 и S = 0. Поскольку у элемента Х вход S = 0, то его выход Q =1 (логика И-НЕ). Сигнал Q подается обратно на элемент Y (вход «В»), и так как R = B = 1, то Q̃ = 0.

Если S становится равен 1 при R = 1, то Q̃ остается равен лог 0, т. е. он не изменяется. Итак, при R =1 схема триггера снова «защелкивается» в состоянии «Сброшен» Q̃ = 0 и Q = 1, сохраняемом при любом сигнале S.

Принцип работы RS триггера

Система, представленная выше, при помощи электромагнитных реле иллюстрирует работу триггера на элементах ИЛИ-НЕ. Однако в современных схемах электромеханические приборы давным-давно не используются, сейчас они собираются из электронных логических элементов на транзисторах, заключенных внутри интегральных микросхем. К тому же для их реализации можно использовать различные базисы. Пример схемы RS триггера на элементах И-НЕ, охваченных положительной обратной связью.

Допустим, что на оба входа R и S подаются единицы. Если верхний элемент И-НЕ выдаст на прямой выход Q логический 0, благодаря положительной обратной связи он поступит на свободный вход нижнего элемента, вследствие чего тот выдаст на инверсном выходе единицу (1). В свою очередь, эта 1 по обратной связи поступает на вход верхнего элемента, тем самым подтверждая 0 на выходе Q. Если же на прямом выходе изначально находится 1, то инверсный, соответственно, выдаст 0, который подтвердит 1 на выходе Q.

Транзисторная схема RS триггера

При подаче на S-вход 0, согласно логической функции И-НЕ, на прямом выходе Q возникнет 1, а на инверсном – 0. Если при этом на вход S снова подать 1, состояние триггера не изменится, так как по таблице истинности И-НЕ при подаче на входы элемента комбинации 0 и 1 либо 0 и 0, на выходе всегда будет 1. Таким образом, триггерная схема сохраняет полученное значение неизменным. Сбросить значение Q обратно в 0 можно, только подав сигнал на сбрасывающий вход R. Практически работу RS триггера можно пронаблюдать, собрав такую схему на транзисторах.

Классификация последовательных схем

Последовательные схемы допускается классифицировать по следующим показателям:

- одноступенчатые защёлки, в которых содержатся элемент памяти и устройство управления, их маркируют буквой Т;

- двухступенчатые ячейки: статического и динамического управления, используются для защиты от гонок сигналов, обозначаются буквами ТТ;

- переключатели, имеющие сложную логику: одно,- и двухступенчатые соты.

Одноступенчатые ячейки применяются в качестве первых ступеней в переключателях ТТ с динамической схемой управления, имеют такое же управление. При самостоятельном использовании управление в большинстве своём статическое.

Двухступенчатые устройства имеют как статическое, так и динамическое управление.

Состояние «Установлен»

RS-переключатель в этом состоянии имеет установленную цепь с Q, равным нулю, и Q¯, равным единице, и независим от управляемого сигнала. При этом на R присутствует ноль, на S – логическая единица.

Состояние «Сброшен»

Это тоже неизменная ситуация. Для её организации необходимо выставить исходные условия. На R подаётся «1», на S – «0». При этом выход Q должен иметь «1», Q¯ – значение «0». Обратные связи обеспечивают и фиксируют независимое от последующих значений на входах значение.

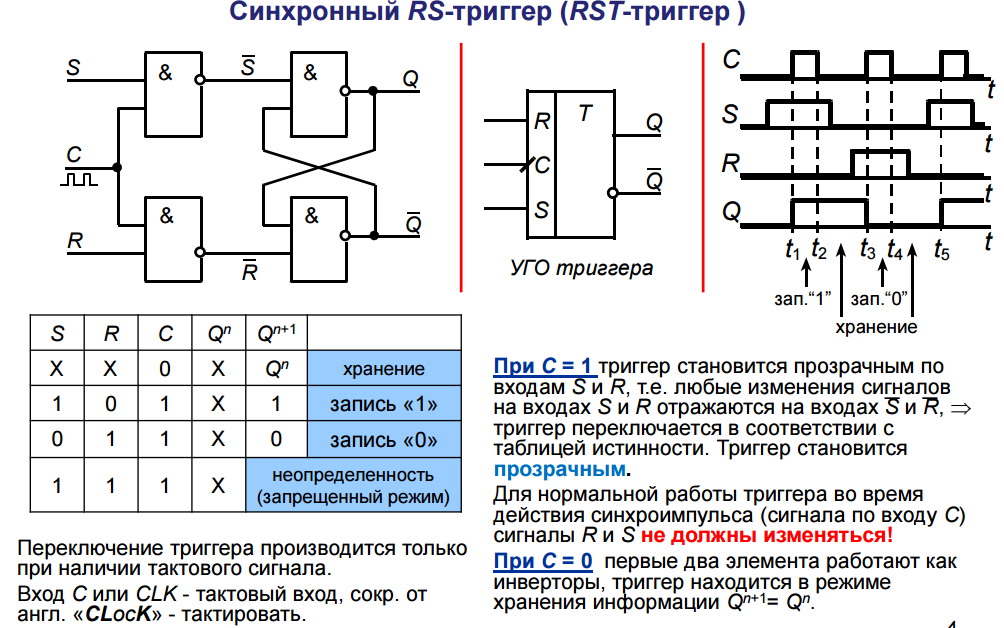

Синхронный RS-триггер

Рассмотрим синхронный RS-триггер (рис. 3.59).

Если на входе С — логический «0», то и на выходе верхнего входного элемента «И-НЕ», и на выходе нижнего будет логическая «1». А это, как отмечалось выше, обеспечивает хранение информации.

Васильев Дмитрий ПетровичПрофессор электротехники СПбГПУЗадать вопрос Таким образом, если на входе С — логический «0», то воздействие на входы R, S не приводит к изменению состояния триггера.

Если же на вход синхронизации С подана логическая единица, то схема реагирует на входные сигналы точно так же, как и рассмотренная ранее (рис. 3.56).

Таблица истинности

Работу триггераРС можно представить в таблице истинности:

- Q устанавливается на логическое значение 1, если применяется 0 на входе S;

- Изменение S-входа на единицу на выходную логику не влияет. 0-импульс был запомнен Q;

- Q сбрасывается на 0 с помощью логического 0, подаваемого на вход R;

- Когда R возвращается к 1, на Q запоминается 0.

Таблица истинности

Для условий 2-й и 3-ей строки таблицы Q̃ является величиной, обратной Q. Однако в первой строке оба входа равны 0, что делает Q̃ = Q = 1, и они не будут являться противоположными логическими состояниями. На практике такое состояние не допускается, так как триггер РС теряет стабильность.

В последней строке на обоих входах присутствует логическая единица, выходы Q̃ и Q будут находиться в противоположных состояниях, но не ясно, какими конкретно значениями будут обладать. Они будут соответствовать запоминаемым с последнего входного импульса.

Помимо применения логики И-НЕ, можно построить простые триггеры, используя два перекрестно соединенных вентиля И-ИЛИ. Схема работает аналогично. Только запрещенное состояние будет при наличии обоих входных сигналов, равных единице.

Типы триггеров и принцип их работы

Существует несколько основных типов триггеров. Перед тем, как разобраться в различиях, следует отметить общее свойство: при подаче питания выход любого устройства устанавливается в произвольное состояние. Если это критично для общей работы схемы, надо предусматривать цепи предустановки. В простейшем случае это RC-цепочка, которая формирует сигнал установки начального состояния.

Читайте также: Описание характеристик, назначение выводов и примеры схем включения линейного стабилизатора напряжения LM317

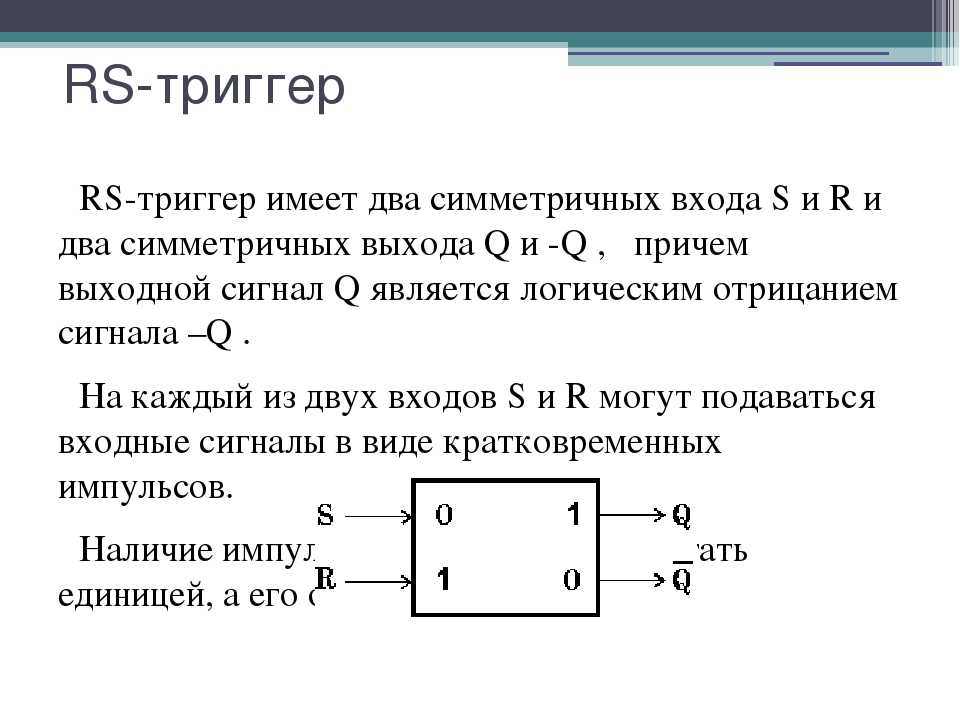

RS-триггеры

Самый распространенный тип асинхронного бистабильного устройства – RS-триггер. Он относится к триггерам с раздельной установкой состояния 0 и 1. Для этого имеется два входа:

- S — set (установка);

- R — reset (сброс).

Имеется прямой выход Q, также может быть инверсный выход Q1. Логический уровень на нём всегда противоположен уровню на Q – это бывает удобно при разработке схем.

При подаче положительного уровня на вход S на выходе Q установится логическая единица (если есть инверсный выход, он перейдет на уровень 0). После этого на входе установки сигнал может меняться как угодно – на выходной уровень это не повлияет. До тех пор, пока единица не появится на входе R. Это установит триггер в состояние 0 (1 на инверсном выводе). Теперь изменение сигнала на входе сброса никак не повлияет на дальнейшее состояние элемента.

Важно! Вариант, когда на обоих входах присутствует логическая единица, является запретным. Триггер установится в произвольное состояние. При разработке схем такой ситуации надо избегать.

RS-триггер можно построить на основе широко распространенных двухвходовых элементов И-НЕ. Такой способ реализуем как на обычных микросхемах, так и внутри программируемых матриц.

Один или оба входа могут быть инверсными. Это означает, что по этим выводам триггер управляется появлением не высокого, а низкого уровня.

Если построить RS-триггер на двухвходовых элементах И-НЕ, то оба входа будут инверсными – управляться подачей логического нуля.

Существует стробируемый вариант RS-триггера. У него имеется дополнительный вход С. Переключение происходит при выполнении двух условий:

- присутствие высокого уровня на входе Set или Reset;

- наличие тактового сигнала.

Такой элемент применяют в случаях, когда переключение надо задержать, например, на время окончания переходных процессов.

D-триггеры

D-триггер («прозрачный триггер», «защелка», latch) относится к категории синхронных устройств, тактируемых по входу С. Также имеется вход для данных D (Data). По функциональным возможностям устройство относится к триггерам с приёмом информации по одному входу.

Пока на входе для синхронизации присутствует логическая единица, сигнал на выходе Q повторяет сигнал на входе данных (режим прозрачности). Как только уровень строба перейдет в состояние 0, на выходе Q уровень останется тем же, что был в момент перепада (защелкнется). Так можно зафиксировать входной уровень на входе в любой момент времени. Также существуют D-триггеры с тактированием по фронту. Они защёлкивают сигнал по положительному перепаду строба.

Читайте также: Как работает микросхема TL431, схемы включения, описание характеристик и проверка на работоспособность

На практике в одной микросхеме могут объединять два типа бистабильных устройств. Например, D и RS-триггер. В этом случае входы Set/Reset являются приоритетными. Если на них присутствует логический ноль, то элемент ведёт себя как обычный D-триггер. При появлении хотя бы на одном входе высокого уровня, выход устанавливается в 0 или 1 независимо от сигналов на входах С и D.

Прозрачность D-триггера не всегда является полезным свойством. Чтобы её избежать, применяются двойные элементы (flip-flop, «хлопающий» триггер), они обозначаются литерами TT. Первым триггером служит обычная защёлка, пропускающая входной сигнал на выход. Второй триггер служит элементом памяти. Тактируются оба устройства одним стробом.

T-триггеры

T-триггер относится к классу счётных бистабильных элементов. Логика его работы проста – он изменяет своё состояние каждый раз, когда на его вход приходит очередная логическая единица. Если на вход подать импульсный сигнал, выходная частота будет в два раза выше входной. На инверсном выходе сигнал будет противофазен прямому.

Так работает асинхронный Т-триггер. Также существует синхронный вариант. При подаче импульсного сигнала на тактирующий вход и при наличии логической единицы на выводе T, элемент ведёт себя так же, как и асинхронный – делит входную частоту пополам. Если на выводе Т логический ноль, то выход Q устанавливается в низкий уровень независимо от наличия стробов.

JK-триггеры

Этот бистабильный элемент относится к категории универсальных. Он может управляться раздельно по входам. Логика работы JK-триггера похожа на работу RS-элемента. Для установки выхода в единицу используется вход J (Job). Появление высокого уровня на выводе K (Keep) сбрасывает выход в ноль. Принципиальным отличием от RS-триггера является то, что одновременное появление единиц на двух управляющих входах не является запретным. В этом случае выход элемента меняет свое состояние на противоположное.

Если выходы Job и Keep соединить, то JK-триггер превращается в асинхронный счётный Т-триггер. Когда на объединённый вход подаётся меандр, на выходе будет в два раза меньшая частота. Как и у RS-элемента, существует тактируемый вариант JK-триггера. На практике применяются, в основном, именно стробируемые элементы такого типа.

Читайте также: Что такое светодиод, его принцип работы, виды и основные характеристики

Триггер типа MS

Рассмотрим принцип построения двухступенчатого триггера, который называют также триггером типа MS (от англ. master, slave, что переводят обычно как «ведущий» и «ведомый»). Его упрощенная структурная схема приведена на рис. 3.60. В схеме имеются два одноступенчатых триггера (ведущий М и ведомый S) и два электронных ключа (Кл1 и Кл2).

Временная диаграмма сигнала синхронизации, поясняющая работу триггера, приведена на рис. 3.61.

Рассмотрим ряд временных интервалов указанной диаграммы:

t < ta — ведущий триггер отключен от информационных входов, ведомый триггер подключен к ведущему;

ta < t < tb — ведущий триггер отключен от информационных входов, ведомый триггер отключен от ведущего;

tb < t < tc — ведущий триггер подключен к информационным входам, ведомый триггер отключен от ведущего. В ведущий триггер записывается информация, поданная на входы;

tc < t < td — ведущий триггер отключен от информационных входов, ведомый триггер отключен от ведущего;

td < t — ведущий триггер отключен от информационных входов, ведомый триггер подключен к ведущему, информация из ведущего триггера переписывается в ведомый. Это происходит сразу после момента времени td и означает, что фактически двухступенчатый триггер срабатывает при изменении сигнала синхронизации от 1 к 0. При этом выходные сигналы определяются теми входными информационными сигналами, которые имели место непосредственно перед отрицательным фронтом сигнала синхронизации.

Триггеры. RS-триггеры. Асинхронный RS-триггер с инверсными входами

ТРИГГЕРЫ

Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит.

Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент.

Триггеры строятся на основе двух инвертирующих усилителей. Обобщенная схема представлена на рис.1.

Рис.1

Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время.

Триггер имеет два выхода: прямой Q

и инверсный

.

Состояние триггера определяют по значению сигнала на прямом выходе

Q.

Значения сигналов на прямом и инверсном выходах всегда противоположны.

Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ.

Читайте также: Онлайн журнал электрика

1.

RS-триггеры ‘

Асинхронные

RS-триггеры.

В асинхронных триггерах срабатывание происходит непосредственно в момент изменения сигнала на информационных входах. Асинхронные

RS

-триггеры являются наиболее простыми. В качестве самостоятельного устройства используются редко, но являются основой для построения более сложных систем.

RS

-триггер — это триггер с раздельной установкой состояний логического нуля и логической единицы. Он имеет два информационных входа

S

и

R..

По входу

S

триггер устанавливается в состояние

Q

=1

(

=0

),

по входу

R—

в состояние

Q

=0

(=

1

).

В зависимости от логической структуры асинхронные

RS

-триггеры бывают с прямыми либо инверсными входами и могут строиться на двух логических элементах: 2ИЛИ-НЕ — триггер с прямыми входами; или на элементах 2И-НЕ — триггер с инверсными входами.

Асинхронный

RS-триггер с прямыми входами

на логических элементах 2ИЛИ-НЕ представлен на рис. 2.

Рис.2.

Логические элементы ИЛИ-НЕ с инвертированием сигнала образуют петлю положительной обратной связи. При таком соединении логическая единица на выходе одного логического элемента (ЛЭ) поступает на вход другого ЛЭ и обеспечивает логический ноль (инвертирование) на его выходе. Логический ноль на выходе ЛЭ, поступая на вход другого, при инвертировании дает логическую 1. Таким образом, выходы Q

и всегда находятся в противоположных состояниях. Соединение элементов по данной схеме позволяет получить цепь с двумя устойчивыми состояниями.

Временные диаграммы, характеризующие работу асинхронного RS

-триггера с прямыми входами, показаны на рис. 3.

Рис.3

Для элементов ИЛИ-НЕ активным является высокий уровень — логическая 1, поэтому в режиме хранения данных на входы этого триггера подаются нулевые значения R

=

S

=0. Установка триггера в нужное состояние производится подачей на соответствующий вход активного уровня единицы. Одновременная подача единицы на оба входа (R и S) приводит к неопределенности. На обоих выходах

Qи

появляются единицы, а после отключения входов (S=R=0) может установиться любое состояние

Состояние «Установлен»

Рассмотрим, как происходит работа RS-триггера в этом состоянии, задаваемом значениями R = 0 и S = 1. Поскольку на вход R элемента И-НЕ Y подан уровень 0, то Q̃ =1 (логика И-НЕ). С выхода Y сигнал Q̃ также подан обратно на элемент X (вход «A»). Поскольку S = A = 1, то Q = 0.

Если устанавливается R = 1, а вход S по-прежнему равен 1, то на входах Y имеем B = 0 и R = 1, а его выход Q̃ =1, т. е. он не изменился. Итак, если S = 1, то RS-схема триггера «защелкивается» в состоянии «Установлен» Q = 0 и Q̃ = 1, а смена сигнала R его не изменяет.

RS-триггер на логических элементах

Простейший способ его сделать – соединить вместе пару двухвходовых логических элементов И-НЕ. При этом обратная связь с выхода одного элемента подается на вход другого (см. схему ниже).

Как правило, в данной схеме входные сигналы показывают инверсными (с верхним подчеркиванием), хотя в дальнейшем при анализе работы используют обозначения прямых (неинвертированных) входов. Это сильно затрудняет понимание логики работы триггера. Поэтому мы не будем вводить инвертирование входов на этапе рассмотрения работы схемы на элементах И-НЕ, а учтем это в дальнейшем при ее модификации.

Сколько входов и выходов имеет RS-триггер? Из схемы выше видно, что он содержит S-вход и R-вход, которые служат, соответственно, для установки и сброса схемы, а также прямой Q и инверсный Q̃ выходы. Но данный простейший триггер относится к виду асинхронных, его условное обозначение показано ниже.

В синхронном устройстве имеется еще и вход C для тактовых импульсов.

JK триггер

Выпрямитель тока

Другие широко распространенные виды логических схем – JK, D и Т, которые являются разработками RS триггера на логических элементах.

Недостатки схемы И-НЕ РС триггера:

- Необходимость избегать условия, когда оба входных сигнала равны 0;

- При изменениях состояния R и S, имеющих единичный входной сигнал, правильное блокирующее действие не всегда происходит.

Для преодоления этих недостатков была разработана схема JK триггера. Его входы являются теми же R и S, но им присвоены буквы J и K по имени изобретателя схемы, чтобы отличить от других триггеров. JK схема отличается от RS триггера тем, что она не имеет неопределенных или запрещенных входных статусов.

JK триггер

В JK добавлена входная схема синхронизации, предотвращающая неопределенное условие вывода, которое может случиться, если R и S равны единице. Поэтому в наличии четыре возможных комбинации ввода: 1, 0, «без изменений» и «переключение». Вход J соответствует S, а K – R. Кроме того, для каждого вентиля имеется третий вход. На выходе остаются Q̃ и Q.

Перекрестная связь RS триггера позволяет использовать ранее неопределенные условия работы триггера, когда оба входных сигнала равны 1, для создания «переключателя», так как два входа могут быть блокированы.

СхемаJK – это триггерSRс обратной связью, который позволяет только одному из его терминалов (SETилиRESET) быть активным в любой момент времени, тем самым устраняя недопустимое условие:

- Если активен терминал SET, вход J блокируется статусом 0 (Q̃) через нижний логический элемент И-НЕ;

- Если в действии терминал RESET, вход К заблокирован статусом 0 через верхний вентиль И-НЕ.

Так как Q̃ и Q всегда разные, они могут использоваться для манипулирования входом. Для JK триггера таблица истинности принимает следующий вид.

Таблица истинности JK триггера

Когда оба входа J и K имеют единицу на входе при высоком тактовом импульсе, схема может переключаться из состояния SET в RESET и наоборот.

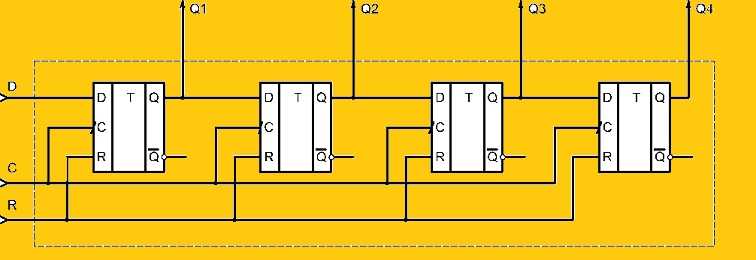

Регистры на триггерах

Так как один переключатель является однобитовой ячейкой памяти, то, чтобы сохранить несколько бит, нужно увеличить количество единичных хранилищ. Цепочка из таких ячеек носит названия регистра. Регистр позволяет временно хранить цифровые данные двоичных разрядов. Количество разрядов зависит от количества однобитовых ячеек.

Схема 4-х разрядного регистра сдвига на триггерах

Использование элементарных электронных цифровых устройств – триггеров, позволяет составлять сложные схемы управления логическими устройствами. Одна элементарная защёлка памяти своим бистабильным состоянием помогает осуществлять самые сложные схемные решения.

Логические триггеры: схемы, классификация, устройство, назначение, применение

Триггер — простейшее последовательностное устройство, которое может находиться в одном из двух возможных состояний и переходить из одного состояния в другое под воздействием входных сигналов. Триггер является базовым элементом последовательностных логических устройств. Входы триггера разделяют на информационные и управляющие (вспомогательные). Это разделение в значительной степени условно. Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации.

{xtypo_quote}Триггеры могут иметь 2 выхода: прямой Q и инверсный Q.{/xtypo_quote}

Триггеры классифицируют по различным признакам, поэтому существует достаточно большое число классификаций. К сожалению, эти классификации не образуют стройной системы, но инженеру необходимо их знать.

JK-триггер

Рассмотрим JK-триггер (от англ. jump иkeep), отличающийся от рассмотренного RS-триггера тем, что появление на обоих информационных входах (J и К) логических единиц (для прямых входов) приводит к изменению состояния триггера. Такая комбинация сигналов для JK-триггера не является запрещенной.

В остальном JK-триггер подобен RS-триггеру, причем роль входа S играет вход J, а роль входа R — вход К.

JK-триггеры реализуют в виде триггеров типа MS или в виде динамических триггеров (т. е. JK-триггеры являются синхронными).

На рис. 3.62 приведено условное графическое обозначение двухступенчатого JK-триггера.

Обратимся к динамическим триггерам. Для них характерно блокирование информационных входов в тот момент, когда полученная информация передается на выход. Нужно отметить, что в отношении реакции на входные сигналы динамический триггер, срабатывающий при изменении сигнала на входе С от 1 к 0, подобен рассмотренному двухступенчатому триггеру, хотя они отличаются внутренним устройством.

Для прямого динамического С-входа используют обозначения, приведенные на рис. 3.63, а, а для инверсного динамического С-входа, используют обозначения, приведенные на рис. 3.63, б.

D-триггер

Рассмотрим D-триггер (от англ. delay), повторяющий на своем выходе состояние входа. Рассуждая чисто теоретически, D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы (рис. 3.64).

Абрамян Евгений ПавловичДоцент кафедры электротехники СПбГПУ Хранение информации в D-триггерах обеспечивается за счет синхронизации, поэтому все реальные D-триггеры имеют два входа: информационный D и синхронизации С. В этом триггере сигнал на входе по сигналу синхронизации записывается и передается на выход. Так как информация на выходе остается неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защелкой.

Условное графическое обозначение D-триггера приведено на рис. 3.65.

Как синхронизировать работу триггера

Подключение двухпортового элемента «И» в последовательную цепь схемы триггера с каждым из входов позволит менять его статус, независимо от состояний на R,- или S-входах. Новый порт С получится при объединении двух портов ячеек «И». В результате доработки статус на выходах Q и Q¯ будет меняться только тогда, когда на С будет приходить высокий потенциал. Предусмотрено подключение генераторов тактовых импульсов на этот новый вход.

Синхронизация триггера

Сводим результаты в таблицу

Мы можем определить состояние сигналов Q и Q̃ по следующей таблице истинности:

| Состояние | S | R | Q | Q̃ | Описание |

| Установка | 1 | 0 | 0 | 1 | Выход Q̃ =1 |

| 1 | 1 | 0 | 1 | без изменений | |

| Сброс | 0 | 1 | 1 | 0 | Выход Q̃ =0 |

| 1 | 1 | 1 | 1 | без изменений | |

| Недопустимое | 0 | 0 | 1 | 1 | состояние ошибки |

Видно, что когда S = R = 1, то Q и Q̃ могут быть равны как 1, так и 0 (но не одновременно!) в зависимости от уровней входов S или R перед возникновением данного состояния выходов. Таким образом, при условии S = R = 1 нельзя изменить состояние выходов Q и Q̃. Оно может измениться только при смене уровня с 1 на 0 на одном из входов.

Значение S = R = 0 является нежелательным или недопустимым состоянием, и его следует избегать. Состояние S = R = 0 вызывает установку обоих выходов Q и Q̃ на уровне 1, в то время как состояние Q̃ всегда должно быть обратно Q. Результатом является то, что триггер теряет контроль над Q и Q̃, и если два входа теперь перейдут к состоянию 1, то схема становится неустойчивой и переключается в неопределенное состояние.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Диаграмма переключения RS-триггера

Сказанное в предыдущем разделе иллюстрирует следующая диаграмма переключения.

Как видно, при S = R = 0 возникает дисбаланс (неопределенность) состояния выходов. Он может привести к переключению одного из выходов быстрее, чем другого, в результате чего произойдет переключение триггера в то или иное состояние, которое может не совпадать с требуемым, и данные будут повреждены. Это неустойчивое состояние обычно называют мета-стабильным.

Таким образом, подобный триггер-защелка может быть переведен в состояние «Установлен» путем подачи 0 на его S-ввод (при наличии 1 на R-вводе) и переведен в состояние «Сброшен» подачей 0 на R-ввод (при наличии 1 на S-вводе). Триггер входит в неопределенное состояние (мета-стабильное), если на оба его входа одновременно подается уровень 0.

Переключение состояния выходов происходит с небольшой задержкой относительно изменения сигнала на одном из входов без использования тактового сигнала. Следовательно, рассмотренная выше схема представляет асинхронный RS-триггер.